# Introduction:

Logic functions can be implemented in several ways. In the past, vacuum tube and relay circuits performed logic functions. Presently logic functions are performed by tiny integrated circuits (ICs). These ICs are small silicon semiconductors sheets called chips, containing the electronic components for the logic gates. The chip is mounted in a plastic container, and connections are welded to external pins may range from 14 in a small IC package to 64 or more in a large one.

## **Objectives:**

- Understand how to use the breadboard to patch up, test your logic design and debug it.

- Wire and operate logic gates such as AND, OR, NOT, NAND, NOR, XOR.

- Understand how to implement simple circuits based on a schematic diagram using logic gates.

## **Theoretical Background:**

### Types of integrated circuits (ICs)

The different sizes of integration of IC chips are usually defined in terms of the number of logic gates in a single IC or package. They are classified in one of the following categories:

- 1. Small-scale integration (SSI) device: contains less than 10 gates in a single package, such as logic gates.

- 2. Medium scale integration (MSI) device: contains 10 -100 gates in a single package, such as adders and decoders.

- 3. Large-scale integration (LSI) device: contains 100 to 10000 gates in a single package, such as processors.

- 4. Very large-scale integration (VLSI) device: contains more than 10000 gates in a single package, such as complex microprocessors chips.

## Logic Families

The types of logic devices are classified in "families", of which the most important are TTL and CMOS. The main families are:

- TTL (Transistor-Transistor Logic) made of bipolar transistors.

- CMOS (Complementary Metal Oxide Semiconductor) made from MOSFETs

- ECL (Emitter Coupled Logic) for extremely high speeds

- NMOS, PMOS for VLSI large scale integrated circuits.

## Subfamilies of TTL Family

There are subfamilies or series of the TTL. Commercial TTL ICs has a number designation that starts with 74 and follows with a suffix that identifies the series type. These subfamilies are: Standard: 74xx, High speed 74hxx, low power 74Lxx, Shottky TTL 74Sxx, Low power shottky 74LSxx, Advanced shottky 74ASxx, Advanced low-power shottky 74ALSxx.

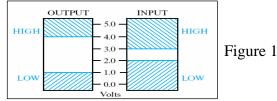

All TTL IC's are designed to operate from 5V power supply. The input and output logic levels are illustrated in the Figure 1.

## Some characteristics of the TTL family

- 1. Power dissipation: It is the amount of power needed by the gate delivered from the power supply. It is equal to 20 mw per gate. Power dissipation is useful to estimate the total power consumption of a system, as an example it will help in portable equipment to know what type of battery might be needed.

- 2. Fan-in: it is the number of inputs that the gate is designed to have, the maximum inputs is 8 inputs per gate.

- 3. Fan-out: it is the maximum number of inputs that can be connected to the output of the gate without affecting its normal operation. It is 12 gates.

- 4. Propagation/time delay: it is the amount of delay between applying the input and the response of the output of the gate. Generally, the propagation delay is in the range of 0.5 to 50 nanoseconds. The total propagation delay time of a logic system will be the delay gate multiplied by the number of gates in series. It is 10 ns per gate.

### Practical TTL Logic Gates

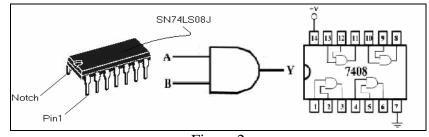

A popular type of IC is illustrated in Figure 2. IC manufacturers refer to this case style as a *dual-in-line package* (DIP). This particular IC is called a 14-pin DIP IC. Just counterclockwise from the notch on the IC is pin 1. A dot (optional) on the top of the IC is another method used to locate pin 1.

Figure 2

Part Number:

Part number is divided into three sections:

- The prefix: the manufacturer's code.

- Core part number: This determines the technology "TTL or CMOS", the device series and the function of a digital IC.

- The trailing letter(s) "the suffix" which is a code used by several manufacturers to design the DIP.

For example, the part number of: SN74LS08J SN: stands for the manufacturer "Texas Instruments" 74: 7400 TTL series LS: low shottky type 08: function of a digital IC J: Ceramic dual-in-line Package

## Breadboard

A breadboard is used to build and test circuits quickly before finalizing any circuit design. The breadboard has series of holes into which ICs can be inserted.

- Breadboard Construction:

- > The breadboard has a series of holes, each containing an electrical contact.

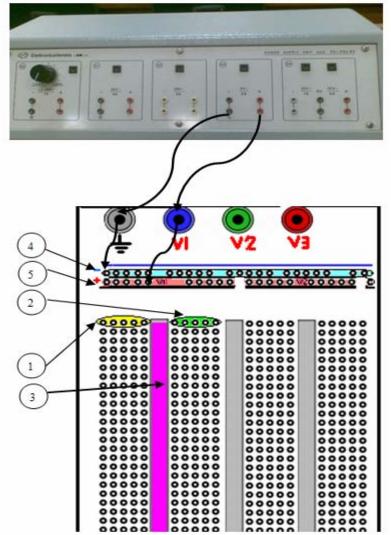

- Holes in the same row (examples highlighted in yellow (1) in Figure3) are electrically connected(they are the same node), holes in other row (highlighted in green (2)) are different node, when you insert a wire into one hole then all the holes in the same node are electrically connected.

- The gap (highlighted in pink (3)) marks a boundary between the electrical connections. A wire inserted in one of the green holes would not be connected to a wire inserted in one of the yellow holes.

- The two top rows of holes at the top highlighted in red and blue are used for power supply connections. The first row (highlighted in blue (4)) is connected to ground, all the holes in this row are electrically connected.

- The second row (highlighted in red (5)) must connected to 5V, there are 40 holes in this row, each 10 holes are grouped together and electrically connected.

- Using a Breadboard

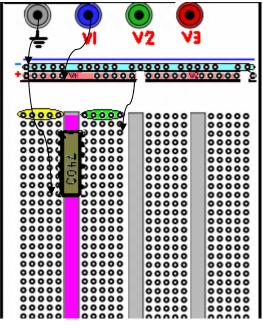

- 1. Before building a circuit, connect 5V from the power supply to V1 (or V2 or V3) in the bread board and 0V the ground of the bread board as shown in the figure below.

Figure 3

- 1. Use wires to connect V1 in the bread board to the red terminal(+), and ground of the bread board to the blue terminal(-).

- 2. Place the IC in the board so that pin 1 should be on the upper left of the board. Half of the legs should be on one side of the pink gap and half on the other.

- 3. Connect pin 14 of the IC chip to  $V_{cc}$  and pin 7 to ground.

- 4. Connect pin 1 and 2 of the IC chip to the input (you can take the input from the two top rows that are connected to the power supply, holes in the first row for logic 0 and holes in the second row for logic 1.

Figure 4

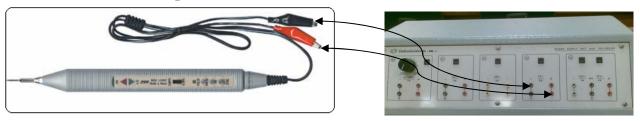

- 5. You can determine the output using the logic probe, logic probe as shown in (Figure5) is a hand-held pen-like probe used for analyzing and troubleshooting the logical states (Boolean 0 or 1) of a digital circuit. It can be used on either TTL or CMOS integrated circuit devices.

- a. Attach red alligator clip to positive side of the power supply.

- b. Attach black alligator clip to a negative side of the power supply.

- c. Place the tip of the probe on the point you want to test. Make sure that the switch is in TTL position.

Figure 5

## Wiring Guidelines:

- Arrange the IC chips on the breadboard so that only short wire connections are needed.

- Try to keep the wire as short as possible to avoid a jungle of wires.

- Try to maintain a low wiring profile so that the pins of the chips can be reached and the chip replaced, if necessary. The best connections are those that lie flat on the board.

Pay extra attention to power and ground. If you find your chips are getting super hot then there is probably a short circuit. Turn off power immediately and wire them correctly.

## Introduction:

This tutorial introduces the basic features of the Quartus II software. It shows how the software can be used to design and implement a circuit specified by using the means of a schematic diagram. It makes use of the graphical user interface to invoke the Quartus II commands.

## **Objectives:**

- Creating a project.

- Design entry using schematic diagram.

- Assigning the circuit inputs and outputs to specific pins on the FPGA.

- Simulating the designed circuit.

- Programming and configuring the FPGA device.

## 1- Getting Started:

Each logic circuit, or sub circuit, being designed with Quartus II software is called a project. The software works on one project at a time and keeps all information for that project in a single directory (folder) in the file system.

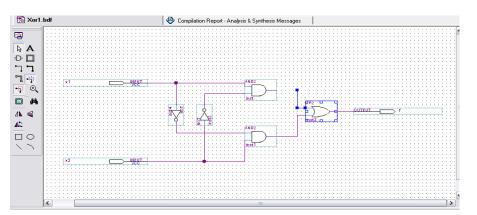

To begin a new logic circuit design, the first step is to create a directory to hold its files. To hold the design files for this lab, we will use a directory Exp2. The running example for this Experiment is a simple circuit for Xor gate (A XOR B = (A& (~B)) | ((~A) &B)).

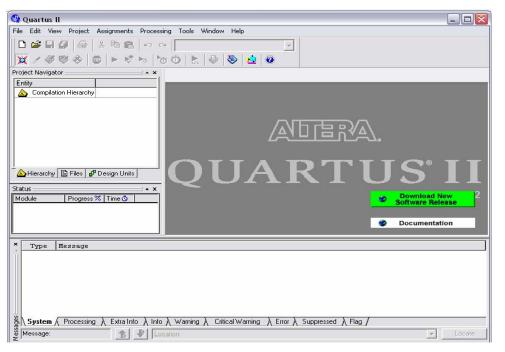

Start the Quartus II software. You should see a display similar to the one in Figure 1. This display consists of several windows that provide access to all the features of Quartus II software, which the user selects with the computer mouse. Most of the commands provided by Quartus II software can be accessed by using a set of menus that are located below the title bar (File, Edit, view, project...).

Figure 1. The main Quartus II display.

### **<u>1.1 Quartus II Online Help</u>**

Quartus II software provides comprehensive online documentation that answers many of the questions that may arise when using the software. The documentation is accessed from the Help menu. To get some idea of the extent of documentation provided, it is worthwhile for the reader to browse through the Help menu. For instance, selecting Help > How to Use Help gives an indication of what type of help is provided. The user can quickly search through the Help topics by selecting Help > Search, which opens a dialog box into which keywords can be entered. Another method, context-sensitive help, is provided for quickly finding documentation for specific topics. While using most applications, pressing the F1 function key on the keyboard opens a Help display that shows the commands available for the application.

## 2- Starting a New Project

To start working on a new design we first have to define a new *design project*. Quartus II software makes the designer's task easy by providing support in the form of a *wizard*.

1. Create a new project; select **File > New Project Wizard** to reach the window in Figure 2b, which asks for the name and directory of the project.

| C.   | Quartus II            |             |                                                                                                                   |

|------|-----------------------|-------------|-------------------------------------------------------------------------------------------------------------------|

| File | Edit View Project     | Assignments | Processing Tools Window Help                                                                                      |

|      | <u>N</u> ew           | Ctrl+N      | -                                                                                                                 |

| B    | <u>O</u> pen          | Ctrl+O      | × 10 0 ≿ 🗶 🕸 👱 🛛                                                                                                  |

|      | Close                 | Ctrl+F4     | • x                                                                                                               |

| 涩    | New Project Wizard    |             |                                                                                                                   |

| R    | Open Project          | Ctrl+J      |                                                                                                                   |

|      | Convert MAX+PLUS II   | Project     |                                                                                                                   |

|      | Save Project          |             |                                                                                                                   |

|      | Clos <u>e</u> Project |             |                                                                                                                   |

|      | Save                  | Ctrl+S      |                                                                                                                   |

|      | Save As               |             |                                                                                                                   |

|      | Save Current Report S | ection As   | DOVINIONAL New     Software Release                                                                               |

| Ī    | Eile Properties       |             | Vers                                                                                                              |

|      | Create ( Update       | •           |                                                                                                                   |

|      | Export                |             |                                                                                                                   |

|      | Convert Programming I | =iles…      |                                                                                                                   |

|      | Page Setup            |             | -                                                                                                                 |

| -    | Print Preview         |             |                                                                                                                   |

|      | Print                 | Ctrl+P      |                                                                                                                   |

|      | Recent Files          | •           |                                                                                                                   |

|      | Recent Projects       | ٠           | $\lambda$ Info $\lambda$ Warning $\lambda$ Critical Warning $\lambda$ Error $\lambda$ Suppressed $\lambda$ Flag / |

| Π    | E <u>×</u> it         | Alt+F4      | Location:                                                                                                         |

| -    |                       |             | J [@⇒∎≠∰ Idle NUM                                                                                                 |

Figure 2a. Creation of a new project.

2. Set the working directory to be Exp2, The project must have a name, which is usually the same as the top-level design entity (schematic circuit) that will be included in the project. Choose *Xor1* as the name for both the project and the top-level entity, as shown in Figure 2b.

| w Project Wizard: Directory,                                                                           | Name, Top-I | _evel Entity [   | page 1 of 5]      |               |

|--------------------------------------------------------------------------------------------------------|-------------|------------------|-------------------|---------------|

|                                                                                                        |             |                  |                   |               |

| What is the working directory for this p                                                               | roject?     |                  |                   |               |

| C:\altera\72\quartus\Exp2                                                                              |             |                  |                   |               |

| What is the name of this project?                                                                      |             |                  |                   |               |

| Yot                                                                                                    |             |                  |                   |               |

| What is the name of the top-level designation and the entity match the entity name in the designation. |             | project? This na | ime is case sensi | tive and must |

| Xor                                                                                                    |             |                  |                   |               |

|                                                                                                        |             |                  |                   |               |

|                                                                                                        | < Back      | Next >           | Finish            | Cancel        |

Figure 2b. Creation of a new project.

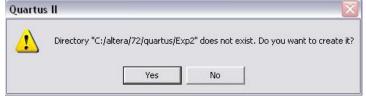

Press **Next**. Since we have not yet created the directory *Exp2*, Quartus II software displays the pop-up box in Figure 3 asking if it should create the desired directory. Click **Yes**, which leads to the window in Figure 4.

Figure 3. Quartus II software can create a new directory for the project.

3. The wizard makes it easy to specify which existing files (if any) should be included in the project. Assuming that we do not have any existing files, click **Next**, which leads to the window in Figure 5.

| ile name | Туре  | Library Desi | ign entry/sy Hi   | DL version                                    | Add All    |

|----------|-------|--------------|-------------------|-----------------------------------------------|------------|

|          | 1,960 | Library 500  | gir ondyr oy prin | <u>, , , , , , , , , , , , , , , , , , , </u> | Bemove     |

|          |       |              |                   |                                               |            |

|          |       |              |                   |                                               | Properties |

|          |       |              |                   |                                               | Up         |

|          |       |              |                   |                                               | Down       |

|          |       |              |                   |                                               |            |

|          |       |              |                   |                                               |            |

|          |       |              |                   |                                               |            |

|          |       |              |                   |                                               |            |

|          |       |              |                   |                                               |            |

|          |       |              | 1                 | >                                             |            |

| :        |       | 1111         |                   |                                               |            |

Figure 4. The wizard can include user-specified design files.

4. We have to specify the type of device in which the designed circuit will be implemented. Choose **CycloneII** as the target device family. We can let Quartus II software select a specific device in the family, or we can choose the device explicitly. We will take the latter approach. From the list of available devices, choose the device called **EP2C70F896C6** which is the FPGA used on Altera's DE2 board. Press **Next**, which opens the window in Figure 6.

|                                         |                  |             |         | - Show in 'Av | ailable dev | ice' list— | _ |

|-----------------------------------------|------------------|-------------|---------|---------------|-------------|------------|---|

| Family: Cyclone II                      |                  |             | -       | Package:      | Any         |            | - |

| Target device                           |                  |             |         | Pin count:    | Any         |            | - |

| <ul> <li>Auto device selecte</li> </ul> | ed by the Fitter |             |         | Fin count:    | PArty       |            | - |

| Specific device selection               | ected in 'Availa | ble devices | :'list  | Speed grad    | le: Any     |            | - |

|                                         |                  |             |         | Show a        | dvanced d   | evices     |   |

|                                         |                  |             |         | HardCo        |             |            |   |

|                                         |                  |             |         | I Harduo      | py compan   | one omly   |   |

| Available devices:                      |                  |             |         |               |             |            |   |

| Name                                    | Core v           | LEs         | User I/ | Memor         | Embed       | PLL        | ~ |

| EP2C50U484C7                            | 1.2V             | 50528       | 294     | 594432        | 172         | 4          | _ |

| EP2C50U484C8                            | 1.2V             | 50528       | 294     | 594432        | 172         | 4          |   |

| EP2C50U48418                            | 1.2V             | 50528       | 294     | 594432        | 172         | 4          |   |

| EP2C70F672C6                            | 1.2V             | 68416       | 422     | 1152000       | 300         | 4          |   |

| EP2C70F672C7                            | 1.2V             | 68416       | 422     | 1152000       | 300         | 4          |   |

| EP2C70F672C8                            | 1.2V             | 68416       | 422     | 1152000       | 300         | 4          |   |

| EP2C70F672I8                            | 1.2V             | 68416       | 422     | 1152000       | 300         | 4          |   |

| EP2C70F896C6                            | 1.2V             | 68416       | 622     | 1152000       | 300         | 4          |   |

| CD0070E00007                            | 1.777            | COALC       | 600     | 1152000       | 200         | 4          |   |

| •                                       |                  |             |         |               |             |            |   |

| - Companion device ——                   |                  |             |         | _             |             |            |   |

|                                         |                  |             | -       |               |             |            |   |

| HardCopy II:                            |                  |             |         |               |             |            |   |

Figure 5. Choose the device family and a specific device

5. The user can specify any third-party tools that should be used. A commonly used term for CAD software for electronic circuits is EDA tools, where the acronym stands for Electronic Design Automation. This term is used in Quartus II messages that refer to third-party tools, which are the tools developed and marketed by companies other than Altera. Since we will rely solely on Quartus II tools, we will not choose any other tools. Press **Next**.

| fool name: KNone>                                            | •             |

|--------------------------------------------------------------|---------------|

| iormat:                                                      |               |

|                                                              | -             |

| Run this tool automatically to synthesize the current design |               |

| imulation                                                    |               |

|                                                              |               |

| ool name:   <none></none>                                    |               |

| format:                                                      | $\overline{}$ |

| Run gate-level simulation automatically after compilation    |               |

| iming Analysis                                               |               |

| -                                                            |               |

|                                                              |               |

| ool name:   <none></none>                                    |               |

Figure 6. Other EDA tools can be specified.

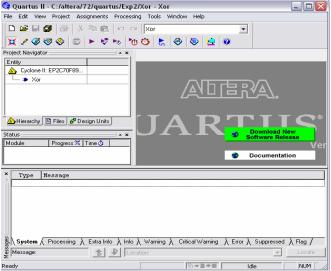

6. A summary of the chosen settings appears in the screen shown in Figure 7. Press **Finish**, which returns to the main Quartus II window, but with Xor specified as the new project, in the display title bar, as indicated in Figure 8.

| w Project Wizard: Summa            | rv [page 5 of 5]                               | [ 🛛 🖓 Quartus II |

|------------------------------------|------------------------------------------------|------------------|

|                                    |                                                | File Edit Vie    |

| When you click Finish, the project | t will be created with the following settings: | D 🚔 🗐            |

| ,,                                 |                                                | 💢 🖉              |

| Project directory:                 |                                                | Project Navigato |

| C:/altera/72/quartus/Exp2/         |                                                | Entity           |

| Project name:                      | Xor                                            | Cyclone I        |

| Top-level design entity:           | Xor                                            |                  |

| Number of files added:             | 0                                              |                  |

| Number of user libraries added:    | 0                                              |                  |

| Device assignments:                |                                                | Hierarchy        |

| Family name:                       | Cyclone II                                     | Status           |

| Device:                            | EP2C70F896C6                                   | Module           |

| EDA tools:                         |                                                |                  |

| Design entry/synthesis:            | <none></none>                                  |                  |

| Simulation:                        | <none></none>                                  | × Type           |

| Timing analysis:                   | <none></none>                                  |                  |

| Operating conditions:              |                                                |                  |

| Core voltage:                      | 1.2V                                           |                  |

| Junction temperature range:        | 0-85 °C                                        |                  |

|                                    | <back next=""> Finish Cancel</back>            | System /         |

|                                    |                                                | Ready            |

Figure 8. The Quartus II display for the created project.

## 3- Design Entry Using the Graphic Editor

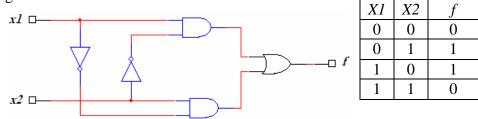

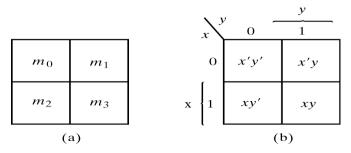

As a design example, we will use the Xor circuit shown in Figure 9. The circuit has two input switches x1 and x2, where a closed switch corresponds to the logic value 1. The truth table for the circuit is also given in the figure.

Figure 9. The Xor function circuit.

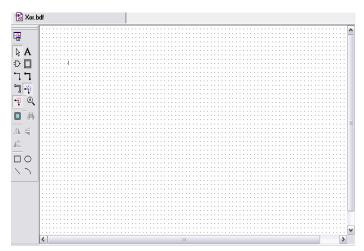

The Quartus II Graphic Editor can be used to specify a circuit in the form of a block diagram. Select **File > New** to get the window in Figure 10, choose **Block Diagram/Schematic File**, and click **OK**. This opens the Graphic Editor window.

| New                                                                                     |           |

|-----------------------------------------------------------------------------------------|-----------|

| Device Design Files Other File                                                          | s         |

| AHDL File<br>Block Diagram/Schematic File                                               |           |

| EDIF File<br>SOPC Builder System<br>State Machine File<br>Verilog HDL File<br>VHDL File |           |

|                                                                                         |           |

|                                                                                         | OK Cancel |

Figure 10. Choose to prepare a block diagram

The first step is to specify a name for the file that will be created. Select **File > Save As** to open the pop-up box depicted in Figure 11. In the box labeled **Save as type choose Block Diagram/Schematic File** (\*.bdf). In the box labeled File name type Xor, to match the name given in Figure 2b, which was specified when the project was created. Put a checkmark in the box Add file to current project. Click **Save**, which puts the file into the directory Exp2 and leads to the Graphic Editor window displayed in Figure 12.

| Save As                |               |                                      |           | $\mathbf{\overline{X}}$ |

|------------------------|---------------|--------------------------------------|-----------|-------------------------|

| Save in:               | Exp2          | •                                    | - 🗈 💣 📰 - |                         |

| My Recent<br>Documents | db            |                                      |           |                         |

| My Documents           |               |                                      |           |                         |

| My Computer            |               |                                      |           |                         |

| ~                      | File name:    | Xor                                  | <u> </u>  | Save                    |

|                        | Save as type: | Block Diagram/Schematic File (*.bdf) | •         | Cancel                  |

|                        |               | Add file to current project          |           |                         |

Figure 11. Name the file.

Figure 12. Graphic Editor window.

### 3.1 Importing Logic-Gate Symbols

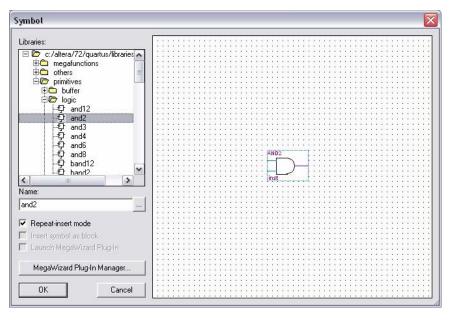

The Graphic Editor provides a number of libraries which include circuit elements that can be imported into a schematic. **Double-click** on the blank space in the Graphic Editor window, or click on the icon in the toolbar that looks like an AND gate. A pop-up box in Figure 13 will appear.

**Expand** the hierarchy in the Libraries box as shown in the figure. First **expand libraries**, and then **expand the library primitives**, followed by **expanding the library logic** which comprises the logic gates. **Select and2**, which is a two-input AND gate, and click **OK**. Now, the AND gate symbol will appear in the Graphic Editor window. Using the mouse, move the symbol to a desirable location and **click** to place it there.

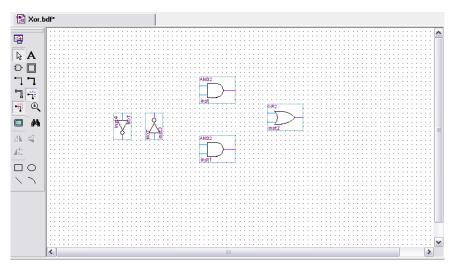

Import the second AND gate, which can be done simply by positioning the mouse pointer over the existing AND-gate symbol, right-clicking, and dragging to make a copy of the symbol. A symbol in the Graphic Editor window can be moved by clicking on it and dragging it to a new location with the mouse button pressed. Next, select or2 from the library and import the OR gate into the diagram. Then, select not and import two instances of the NOT gate. Rotate the NOT gates into proper position by using the "Rotate left 90" icon. Arrange the gates as shown in Figure 14.

Figure 13. Choose a symbol from the library.

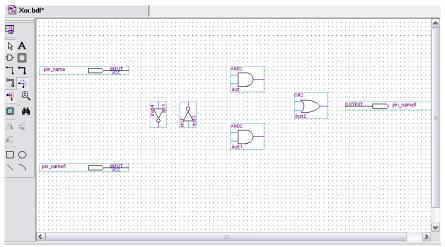

Figure 14. Import the gate symbols into the Graphic Editor window.

## **3.2 Importing Input and Output Symbols**

Having entered the logic-gate symbols, it is now necessary to enter the symbols that represent the input and output ports of the circuit. Use the same procedure as for importing the gates, but choose the port symbols from the library primitives/pin. Import two instances of the input port and one instance of the output port, to obtain the image in Figure 15.

Figure 15. Import the input and output pins.

Assign names to the input and output symbols as follows. Make sure nothing is selected by clicking on an empty spot in the Graphic Editor window. **Point** to the word pin\_name on the top input symbol and **double-click** the mouse. The dialog box in Figure 16 will appear. **Type the pin name**, x1, and click **OK**. Similarly, assign the name x2 to the other input and f to the output. Alternatively, it is possible to change the name of an element by selecting it first, and then double-clicking on the name and typing a new one directly.

| in Properties                     |                                                                                                        | ×     |

|-----------------------------------|--------------------------------------------------------------------------------------------------------|-------|

| General Format                    | 1                                                                                                      |       |

| To create multi<br>"name[30]"), ( | ple pins, enter a name in AHDL bus notation (for example,<br>or enter a comma-separated list of names. |       |

| Pin name(s):                      | x1                                                                                                     | _     |

| Default value:                    | VCC •                                                                                                  |       |

|                                   |                                                                                                        |       |

|                                   |                                                                                                        |       |

|                                   |                                                                                                        |       |

|                                   |                                                                                                        |       |

|                                   |                                                                                                        |       |

|                                   | ОК С                                                                                                   | ancel |

|                                   |                                                                                                        |       |

Figure 16. Naming of a pin.

#### **3.3 Connecting Nodes with Wires**

The symbols in the diagram have to be connected by drawing lines (wires). **Click on the icon** in the toolbar to activate the Orthogonal Node Tool. **Position the mouse** pointer over the right edge of the x1 input pin. **Click and hold** the mouse button and **drag** the mouse to the right until the drawn line reaches the pinstub on the top input of the AND gate. **Release** the mouse button, which leaves the line connecting the two pinstubs. Next, draw a wire from the input pinstub of the leftmost NOT gate to touch the wire that was drawn above it. Note that a dot will appear indicating a connection between the two wires.

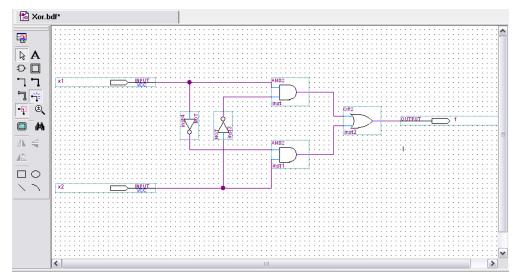

Use the same procedure to draw the remaining wires in the circuit. If a mistake is made, a wire can be selected by clicking on it, and removed by pressing the Delete key on the keyboard. Upon completing the diagram, click on the icon, to activate the Selection Tool. Now, changes in the appearance of the diagram can be made by selecting a particular symbol or wire and either moving it to a different location or deleting it. The final diagram is shown in Figure 17; **save it.**

Figure 17. The completed schematic diagram.

## 4- Compiling the Designed Circuit

The entered schematic diagram file, Xor.bdf, is processed by several Quartus II tools that analyze the file, synthesize the circuit, and generate an implementation of it for the target chip. These tools are controlled by the application program called the Compiler.

Run the Compiler by selecting **Processing > Start Compilation**, or by clicking on the toolbar icon that looks like a **purple triangle**. As the compilation moves through various stages, its progress is reported in a window on the left side of the Quartus II display. Successful (or unsuccessful) compilation is indicated in a pop-up box.

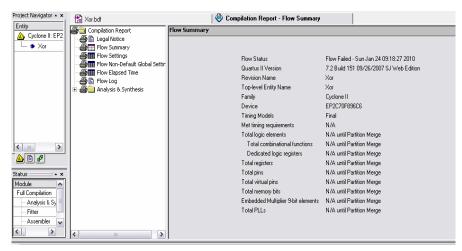

Acknowledge it by clicking **OK**, which leads to the Quartus II display in Figure 18. In the message window, at the bottom of the figure, various messages are displayed. In case of errors, there will be appropriate messages given.

When the compilation is finished, a compilation report is produced. A window showing this report is opened automatically, as seen in Figure 18. The window can be resized, maximized, or closed in the normal way, and it can be opened at any time either by selecting **Processing > Compilation Report** or by clicking on the icon.

The report includes a number of sections listed on the left side of its window. Figure 18 displays the Compiler Flow Summary section, which indicates that only one logic element and three pins are needed to implement this tiny circuit on the selected FPGA chip.

| Project Navigator • ×                                                                       | 📸 Xor1.bdf                                                        | 🕘 Compilation Report - Flow Summary                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Entity<br>Cyclone II: EP2<br>Status<br>Status<br>Ful Completion<br>Analysis 8, 5, =<br>File |                                                                   | Compilation Report - Flow Summary Flow Summary Flow Status Quartus II Version Revision Name Top-level Entity Name Family Device Timing Models Met timing requirements Total Gigic elements Total combinational functions Dedicated logic registers Total registers Total priss Total PLLs | Successful - Sun Jan 24 11:20:25 2010<br>7.2 Build 151 09/26/2007 SJ Web Edition<br>Xor1<br>Cyclone II<br>EP22/DF9960C6<br>Final<br>Yes<br>1 / 88.416 (<1 %)<br>1 / 68.416 (<1 %)<br>0 / 68.416 (0 %)<br>0<br>0 / 1.152.000 (0 %)<br>0 / 1.152.000 (0 %)<br>0 / 300 (0 %)<br>0 / 4 (0 %) |

|                                                                                             | <(>)                                                              |                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                          |

| × Type<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓<br>↓                     | Info: Longest tpd from source ;<br>Info: Quartus II Classic Timin | c Timing Analyzer<br>ead_settings_files=offwrite_settings_files=<br>in "Xi" to destination pin "2" is 12.189 ns<br>A malyzer was successful. 0 errors, 0 warning<br>on was successful. 0 errors, 6 warnings                                                                                                                                                                   |                                                                                                                                                                                                                                                                                          |

Figure 18. Display after a successful compilation.

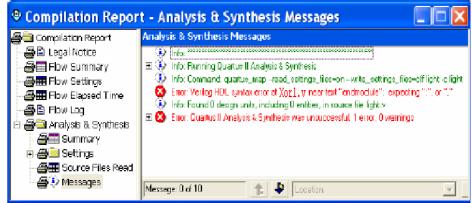

In the case of unsuccessful compilation, Figure 19 shows the compilation report (Flow Summary).

Figure 19. Compilation report for the failed design.

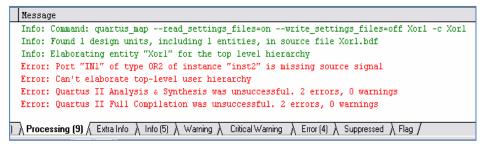

In the message tab, all errors will be shown, see Figure 20

Figure 20. Error messages.

Figure 21. Identifying the location of the error.

After correcting all errors, recompile the circuit.

## 5- Pin Assignment

During the compilation above, the Quartus II Compiler was free to choose any pins on the selected FPGA to serve as inputs and outputs. However, the DE2 board has hardwired connections between the FPGA pins and the other components on the board. We will use two toggle switches, labeled **SW10** and **SW11**, to provide the external inputs, x1 and x2, to our example circuit. These switches are connected to the FPGA pins **W5** and **V10**, respectively. We will connect the output f to the red light-emitting diode labeled **LEDR10**, which is hardwired to the FPGA pin **AC13**.

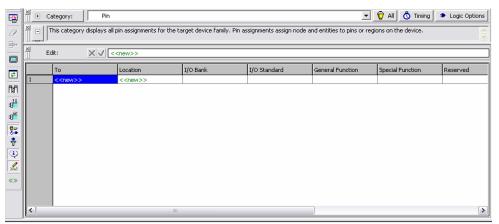

Pin assignments are made by using the Assignment Editor. Select Assignments > Assignment Editor to reach the window in Figure 22.

Figure 22. The Assignment Editor window.

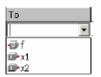

**Under Category select Pin. Double-click on the entry** <<**new**>> which is highlighted in blue in the column labeled To. The drop-down menu in Figure 23 will appear. **Click on x1** as the first pin to be assigned; this will enter x1 in the displayed table. Follow this by **double-clicking** on the box to the right of this new x1 entry, in the column labeled **Location.** Now, the drop-down menu in Figure 24 appears.

Figure 23. The drop-down menu displays the input and output names.

Scroll down and select **PIN\_W5**. Instead of scrolling down the menu to find the desired pin, you can just **type the name of the pin (W5)** in the Location box. Use the same procedure to assign input x2 to pin V10 and output f to pin AC13, which results in the image in Figure 25.

|   | То                | Location | I/O Bank   |         | I/O Standard | General Function   | Special Fund |

|---|-------------------|----------|------------|---------|--------------|--------------------|--------------|

| 1 | IIII ×1           | PIN_W5   | [          |         | 3.3-V LVTTL  |                    |              |

| 2 | < <new>&gt;</new> | PIN_W5   | I/O Bank 1 | Row I/C | )            |                    | ~            |

|   |                   | PIN_W6   | I/O Bank 1 | Row I/C | )            |                    |              |

|   |                   | PIN_W7   | I/O Bank 1 | Row I/C | D LVDS17n    |                    |              |

|   |                   | PIN_W8   | I/O Bank 1 | Row I/C | ) LVDS17p, C | DPCLK1/DQS3L/CQ3L# |              |

|   |                   | PIN_W9   | I/O Bank 1 | Row I/C | ) LVDS18p    |                    |              |

|   |                   | PIN_W10  | I/O Bank 1 | Row I/C | D LVDS18n    |                    |              |

|   |                   | PIN_W21  | I/O Bank 6 | Row I/C | D LVDS177p   |                    |              |

|   |                   | PIN_W22  | I/O Bank 6 | Row I/C | D LVDS177n   |                    |              |

|   |                   | PIN_W23  | I/O Bank 6 | Row I/C | D LVDS179n   |                    |              |

|   |                   | PIN_W24  | I/O Bank 6 | Row I/C | D LVDS179p   |                    |              |

|   |                   | PIN_W25  | I/O Bank 6 | Row I/C | D LVDS175n   |                    |              |

|   |                   | PIN_W26  | I/O Bank 6 | Row I/C | )            |                    |              |

|   |                   | PIN_W27  | I/O Bank 6 | Row I/C | D LVDS171n   |                    |              |

|   |                   | PIN_W28  | I/O Bank 6 | Row I/C | D LVDS171p   |                    |              |

| < |                   | PIN_W29  | I/O Bank 6 | Row I/C | D LVDS169n   |                    | <b>~</b>     |

Figure 24. The available pins.

|   |                   | Pin<br>I the device for the curre | ent node(s) and/or pin(s | ).           | <u>•</u>         | All 💍 Timing     | Logic Options |

|---|-------------------|-----------------------------------|--------------------------|--------------|------------------|------------------|---------------|

| × | Edit: 🗙 🔪         | / < <new>&gt;</new>               |                          |              |                  |                  |               |

|   | То                | Location                          | I/O Bank                 | I/O Standard | General Function | Special Function | Reserved      |

| 1 | iii≥×1            | PIN_W5                            | 1                        | 3.3-V LVTTL  | Row I/O          |                  |               |

| 2 |                   | PIN_V10                           | 1                        | 3.3-V LVTTL  | Row I/O          | LVDS23p          |               |

| 3 | r∰f               | PIN_AC13                          | 8                        | 3.3-V LVTTL  | Column I/O       |                  |               |

| 4 | < <new>&gt;</new> | < <new>&gt;</new>                 |                          |              |                  |                  |               |

| < |                   |                                   | 101                      |              |                  |                  | ۵             |

Figure 25. The complete assignment.

To save the assignments made, choose File > Save. You can also simply close the Assignment Editor window, in which case a pop-up box will ask if you want to save the changes to assignments; click Yes. **Recompile the circuit**, so that it will be compiled with the correct pin assignments.

# 6- Simulating the Designed Circuit

Before implementing the designed circuit in the FPGA chip on the DE2 board, it is prudent to simulate it to ascertain its correctness. Quartus II software includes a simulation tool that can be used to simulate the behavior of a designed circuit. Before the circuit can be simulated, it is necessary to create the desired waveforms, called **test vectors**, to represent the input signals. It is also necessary to specify which outputs, as well as possible internal points in the circuit, the designer wishes to observe. The simulator applies the test vectors to a model of the implemented circuit and determines the expected response. We will use the Quartus II Waveform Editor to draw the test vectors, as follows:

1. Open the Waveform Editor window by selecting **File > New>Other Files** tab, which gives the window shown in Figure 26.Choose **Vector Waveform File** and click **OK**.

| New                                                                                                                                                                                                                                                                                                                                            |           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Device Design Files Other Files AHDL Include File Block Symbol File Chain Description File Hexadecimal (Intel-Format) File In-System Sources and Probes Editor File Logic Analyzer Interface File Memory Initialization File SignalTa p II Logic Analyzer File Sympasys Design Constraints File Tcl Script File Text File Vector Waveform File |           |

|                                                                                                                                                                                                                                                                                                                                                | OK Cancel |

Figure 26. Need to prepare a new file.

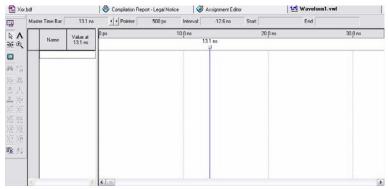

2. The Waveform Editor window is depicted in Figure 27. Save the file under the name Xor.vwf; note that this changes the name in the displayed window. Set the desired simulation to run from 0 to 200 ns by selecting Edit > End Time and entering 200 ns in the dialog box that pops up. Selecting View > Fit in Window displays the entire simulation range of 0 to 200 ns in the window, as shown in Figure 28. You may wish to resize the window to its maximum size.

Figure 27. The Waveform Editor window.

| 3                                            | Master Time Bar: | 13.1 ns             | <ul> <li>Pointer:</li> </ul> | 2.67 ns | Interval: | -10.43 ns | Start: |                       | End: |      |         |

|----------------------------------------------|------------------|---------------------|------------------------------|---------|-----------|-----------|--------|-----------------------|------|------|---------|

| ₩                                            | Name             | Value at<br>13.1 ns | 0 ps<br>13.1 ns              | 40.0 ns |           | 80.0 ns   | 1      | 120 <sub>,</sub> 0 ns | 160  | 0 ns | 200.0 r |

| ■ No B A K K K K K K K K K K K K K K K K K K |                  |                     |                              |         |           |           |        |                       |      |      |         |

Figure 28. The augmented Waveform Editor window.

3. Next, we want to include the input and output nodes of the circuit to be simulated. Click **Edit > Insert> Insert Node or Bus** to open the window in Figure 29.

| Insert Node or Bus 🛛 🔀 |                               |   |             |  |  |  |  |

|------------------------|-------------------------------|---|-------------|--|--|--|--|

| Name:                  | 1                             |   | ОК          |  |  |  |  |

| Туре:                  | INPUT                         | • | Cancel      |  |  |  |  |

| Value type:            | 9-Level                       | • | Node Finder |  |  |  |  |

| Radix:                 | ASCII                         | • |             |  |  |  |  |

| Bus width:             | 1                             |   |             |  |  |  |  |

| Start index:           | 0                             |   |             |  |  |  |  |

| 🔲 Display gr           | ay code count as binary count |   |             |  |  |  |  |

Figure 29. The Insert Node or Bus dialogue.

It is possible to type the name of a signal (pin) into the Name box, but it is easier to click on the **Node Finder** button to open the window in Figure 30. The Node Finder utility has a filter used to indicate what type of nodes are to be found. Since we are interested in input and output pins, **set the filter to Pins:** all. **Click the List button** to find the input and output nodes as indicated on the left side of the figure.

| lode Finder        |                                            |                         |               |

|--------------------|--------------------------------------------|-------------------------|---------------|

| Named: ×           | Filter: Pins: all                          | Customize               | List OK       |

| Look in: Kor1      |                                            | 💌 🔽 Include subentities | Stop Cancel   |

| Nodes Found:       |                                            | Selected Nodes:         |               |

| Name               | Assignments T                              | Name                    | Assignments T |

| @f<br>I™x1<br>I™x2 | PIN_ACI3 C<br>PIN_W5 Ir<br>PIN_V10 Ir<br>X |                         |               |

| <                  |                                            | <                       | ۲             |

Figure 30. Selecting nodes to insert into the Waveform Editor.

Click on the x1 signal in the Nodes Found box in Figure 30, and then **click the** |>| **sign** to add it to the Selected Nodes box on the right side of the figure. Do the same for x2 and f. Click **OK** to close the Node Finder window, and then click **OK** in the window of Figure 29. This leaves a fully displayed Waveform Editor window, as shown in Figure 31. If you did not select the nodes in the same order as displayed in Figure 31, it is possible to rearrange them. To move a waveform up or down in the Waveform Editor window, click on the node name (in the Name column) and release the mouse button. The waveform is now highlighted to show the selection. Click again on the waveform and drag it up or down in the Waveform Editor.

| 👌 Xor1.b                    | df         |         |                     | 10              | Waveform1.v | wf*       |           |        |                       |      |                       |         |

|-----------------------------|------------|---------|---------------------|-----------------|-------------|-----------|-----------|--------|-----------------------|------|-----------------------|---------|

| ۱<br>۱                      | faster Tim | e Bar:  | 13.1 ns             | Pointer:        | 2.37 ns     | Intervalt | -10.73 ns | Start: |                       | End: |                       |         |

| A<br>E @                    |            | Name    | Value at<br>13.1 ns | 0 ps<br>13.1 ns | 40.0 ns     |           | 80.0 ns   |        | 120 <sub>,</sub> 0 ns |      | 160 <sub>,</sub> 0 ns | 200.0 r |

|                             | <b>D</b>   | x1      | A O                 |                 |             |           |           |        |                       |      |                       |         |

| A R H                       | ▶1         | x2<br>f | A 0<br>A X          |                 |             |           |           |        |                       |      |                       |         |

| ※<br>1、図 単語 返 (2)<br>を<br>ま |            |         |                     |                 |             |           |           |        |                       |      |                       |         |

Figure 31. The nodes needed for simulation.

4. We will now specify the logic values to be used for the input signals x1 and x2 during simulation. The logic values at the output f will be generated automatically by the simulator. To make it easy to draw the desired waveforms, the Waveform Editor displays (by default) vertical guidelines and provides a drawing feature that snaps on these lines (which can otherwise be invoked by choosing **View** > **Snap to Grid**). Observe also a solid vertical line, which can be moved by pointing to its top and dragging it horizontally. This reference line is used in analyzing the timing of a circuit; move it to the time = 0 position.

The waveforms can be drawn using the **Selection Tool**, which is activated by selecting the icon  $\searrow$  in the toolbar, or the Waveform Editing Tool, which is activated by the icon  $\cancel{3}$ .

To simulate the behavior of a large circuit, it is necessary to apply a sufficient number of input valuations and observe the expected values of the outputs. In a large circuit the number of possible input valuations may be huge, so in practice we choose a relatively small (but representative) sample of these input valuations.

However, for our tiny circuit we can simulate all different combinations (00, 01, 10, 11) given in Figure 9. We will use four 50-ns time intervals to apply the four test vectors. We can generate the desired input waveforms as follows. **Click on the waveform name for the x1 node**. Once a waveform is selected, the editing commands in the Waveform Editor can be used to draw the desired waveforms. Commands are available for setting a selected signal to 0, 1, unknown (X), high impedance (Z), don't care (DC), inverting its existing value (INV), or defining a clock waveform. Each command can be activated by using the **Edit** > **Value** command or via the toolbar for the Waveform Editor. The Edit menu can also be opened by **right-clicking on a waveform name**.

Set x1 to 0 in the time interval 0 to 100 ns, which is probably already set by default. Next, set x1 to 1 in the time interval 100 to 200 ns. Do this by **pressing the mouse at the start of the interval and dragging it to its end**, which highlights the selected interval, and **choosing the logic value 1 in the toolbar**. Make x2 = 1 from 50 to 100 ns and also from 150 to 200 ns, which corresponds to the truth table in Figure 9. This should produce the image in Figure 32. Observe that the output f is displayed as having an unknown value at this time, which is indicated by a hashed pattern; its value will be determined during simulation. **Save the file as Xor1.vwf**.

Figure 32. Setting of test values.

#### **6.1 Performing the Simulation**

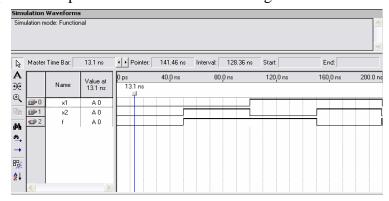

A designed circuit can be simulated in two ways. The simplest way is to assume that logic elements and interconnection wires in the FPGA are perfect, thus causing no delay in propagation of signals through the circuit. This is called **Functional simulation**. A more complex alternative is to take all propagation delays into account, which leads to **Timing simulation**. Typically, functional simulation is used to verify the functional correctness of a circuit as it is being designed. This takes much less time, because the simulation can be performed simply by using the logic expressions that define the circuit.

#### 6.1.1 Functional Simulation

To perform the functional simulation select **Assignments > Settings** to open the Settings window, on the left side of this window click on **Simulator Settings** to display the window in Figure 33, **choose Functional as the simulation mode**, **choose Xor1.vwf as the simulation input**, and click **OK**. The Quartus II simulator takes the inputs and generates the outputs defined in the Xor.vwf file.

| Category:                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General<br>Files<br>Libraries<br>Device<br>Operating Sattings and Conditions<br>Compilation Process Settings<br>EDA Tool Settings<br>Filter Settings<br>Timing Analysis Synthesic Sattings<br>Timing Analysis Settings<br>Assembler<br>Design Assistant<br>Signal Tap II Logic Analyzer<br>Logic Analyzer Interface<br>Simulator Settings<br>PowerPlay Power Analyzer Settings | Select simulation options. Simulation mode: Functional Simulation input: Xor1.vwf C Run simulation until all vector stimuli are used C End simulation at Gittch filtering options: Auto More Settings Description: |

|                                                                                                                                                                                                                                                                                                                                                                                | Specifies the type of simulation to perform for the current Simulation focus.                                                                                                                                      |

Figure 33. Specifying the simulation mode.

Before running the functional simulation it is necessary to create the required netlist; select **Processing > Generate Functional Simulation Netlist**. A simulation run is started by **Processing > Start Simulation**. At the end of the simulation, Quartus II software indicates its Successful completion and displays a **Simulation Report** illustrated in Figure 34. If your report window does not show the entire simulation time range, **click on the report window** to select it and choose **View > Fit in Window**. Observe that the output f is as specified in the truth table of Figure 9.

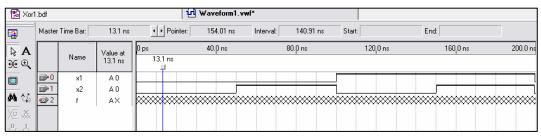

Figure 34. The result of functional simulation.

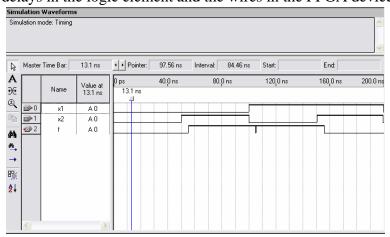

#### 6.1.2 Timing Simulation

Having ascertained that the designed circuit is functionally correct, we should now perform the timing simulation to see how it will behave when it is actually implemented in the chosen FPGA device. Select Assignments > Settings > Simulator Settings to get to the window in Figure 33, choose Timing as the simulation mode, choose Xor1.vwf as the simulation input, and click OK. Run the simulator, which should produce the waveforms in Figure 35. Observe that there is a delay of about 6 ns in producing a change in the signal f from the time when the input signals, x1 and x2, change their values. This delay is due to the propagation delays in the logic element and the wires in the FPGA device.

Figure 35. The result of timing simulation.

# 7- Programming and Configuring the FPGA Device

The FPGA device must be programmed and configured to implement the designed circuit. The required configuration file is generated by the Quartus II Compiler's Assembler module. Altera's DE2 board allows the configuration to be done in two different ways, known as JTAG and AS modes. The configuration data is transferred from the host computer (which runs the Quartus II software) to the board by means of a cable that connects a USB port on the host computer to the leftmost USB connector on the board. To use this connection, it is necessary to have the USB-Blaster driver installed. Before using the board, make sure that the USB cable is properly connected and turn on the power supply switch on the board.

In the JTAG mode, the configuration data is loaded directly into the FPGA device. The acronym JTAG stands for Joint Test Action Group. This group defined a simple way for testing digital circuits and loading data into them, which became an IEEE standard. If the FPGA is configured in this manner, it will retain its configuration as long as the power remains turned on. The configuration information is lost when the power is turned off. The second possibility is to use the Active Serial (AS) mode. In this case, a configuration device that includes some flash memory is used to store the configuration data. Quartus II software places the configuration data into the configuration device on the DE2 board. Then, this data is loaded into the FPGA upon power-up or reconfiguration.

Thus, the FPGA need not be configured by the Quartus II software if the power is turned off and on. The choice between the two modes is made by the RUN/PROG switch on the DE2 board. The RUN position selects the JTAG mode, while the PROG position selects the AS mode.

### 7.1 JTAG Programming

The programming and configuration task is performed as follows. Flip the RUN/PROG switch into the RUN position. Select Tools > Programmer to reach the window in Figure 36. Here it is necessary to specify the programming hardware and the mode that should be used. If not already chosen by default, select JTAG in the Mode box.

| 🖏 Quartus II - D:/altera/quartus/Exp2/> | Kor1 - Xor1 - [Xor1                                                       | .cdf]               |                  |              |            |                       |             |                 |  |

|-----------------------------------------|---------------------------------------------------------------------------|---------------------|------------------|--------------|------------|-----------------------|-------------|-----------------|--|

| File Edit View Project Assignments Pro  | ocessing Tools Windo                                                      | ow Help             |                  |              |            |                       |             |                 |  |

| D 🗳 🖬 🕼 🕼 🐇 🖪 🖻 🖉 🕫                     | 🗠 Xor1                                                                    | - 💥                 | 2 🏈 🦁 🚳 🖉        | )   F 🕏 H    | s 🔤 🐨 👌    | : 🕘 💐                 | > 👱         | 0               |  |

| Status × Kongress % Time §              | 🌵 Xor1.v                                                                  | 🛛 🕹 Compilation 🗍 🅸 | Verilog2.v 👘 🧳 / | Assignment E | 🖸 Xor1.vwf | 🛛 🕘 Sir               | nulation R. | 🖻               |  |

| Simulator 100 % 00:00:06                | 🔔 Hardware Setup                                                          | USB-Blaster [USB-0] |                  | Mode: JTA    | 3          | ▼ Pro                 | gress:      |                 |  |

|                                         | Enable real-time ISP to allow background programming (for MAX II devices) |                     |                  |              |            |                       |             |                 |  |

|                                         | 🏓 Start                                                                   | File                | Device           | Checksum     | Usercode   | Program/<br>Configure | Verify      | Blank-<br>Check |  |

|                                         | 🖿 Stop                                                                    | Xor1.sof            | EP2C70F896       | 00606161     | FFFFFFF    | V                     |             |                 |  |

|                                         | \mu Auto Detect                                                           |                     |                  |              |            |                       |             |                 |  |

|                                         | 🗙 Delete                                                                  |                     |                  |              |            |                       |             |                 |  |

|                                         | 🍰 Add File                                                                |                     |                  |              |            |                       |             |                 |  |

|                                         | 🔛 Change File                                                             |                     |                  |              |            |                       |             |                 |  |

|                                         | Save File                                                                 |                     |                  |              |            |                       |             |                 |  |

|                                         | 😂 Add Device                                                              |                     |                  |              |            |                       |             |                 |  |

|                                         | 📫 Up                                                                      |                     |                  |              |            |                       |             |                 |  |

|                                         | 🔑 Down                                                                    |                     |                  |              |            |                       |             |                 |  |

|                                         |                                                                           |                     |                  |              |            |                       |             |                 |  |

Figure 36. The Programmer window.

Also, if the USB-Blaster is not chosen by default, **press the Hardware Setup...** button and **select the USB-Blaster** in the window that pops up, as shown in Figure 37.

| ardware Setup<br>Hardware Settings JTAG Se<br>Select a programming hardw<br>hardware setup apples only | vare setup to use whe |       | vice». This programming |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------|-----------------------|-------|-------------------------|--|--|--|--|--|

| Currently selected hardware: USB-0]                                                                    |                       |       |                         |  |  |  |  |  |

| Hardware<br>USB-Blaster                                                                                | Local                 | USB-0 | Remove Hardware         |  |  |  |  |  |

|                                                                                                        |                       |       | Dove                    |  |  |  |  |  |

Figure 37. The Hardware Setup window.

In Figure 36, observe that the configuration file Xor1.sof is listed in the window. If the file is not already listed, then click **Add File** and select it. This is a binary file produced by the Compiler's Assembler module, which contains the data needed to configure the FPGA device. The extension .sof stands for SRAM Object File. Note also that the device selected is **EP2C70F896C6**, which is the FPGA device used on the DE2 board. **Click on the Program/Configure check box**. Now, **press Start button**. A LED on the board will light up when the configuration data has been downloaded successfully. If you see an error reported by Quartus II software indicating that programming failed, check to ensure that the board is properly powered on.

## Introduction:

Verilog HDL is a hardware description language used to design electronic systems. Verilog HDL allows designers to design at various levels of abstraction. It is the most widely used HDL with a user community of more than 50,000 active designers.

This tutorial shows how the Quartus II software can be used to design and implement a circuit specified by using the Verilog hardware description language.

## **Objectives:**

- Creating a project using Quartus II software.

- Design entry using Verilog code.

- Assigning the circuit inputs and outputs to specific pins on the FPGA.

- Simulating the designed circuit.

- Programming and configuring the FPGA device.

## ➢ What is Verilog?

Verilog is one of the two major Hardware Description Languages (HDL) used by hardware designers in industry and academia. VHDL is the other one.

The Verilog language describes a digital system as a set of modules. Each of these modules has input(s) and output(s). Usually we place one module per file but that is not a requirement.

*<u>Note</u>*: Verilog is **case sensitive**

### The structure of a module is the following:

```

module <module name> (<port list>);

<declares>

<module items>

endmodule

```

- The **<module name>** is an identifier that uniquely names the module.

- The **<port list>** is a list of input and output ports.

- The <declares> section specifies data objects as inputs, outputs, or wires.

- The **<module items>** may be assignments or instances of modules.

Modules can represent pieces of hardware ranging from simple gates to complete systems. Modules can either be specified **behaviorally or structurally** (or a combination of the two).

- A **behavioral specification** defines the behavior of a digital system (module) using traditional programming language constructs, e. g., **ifs**, **while**s, **assignment statements**.

#### **Example:**

```

// Behavioral Model of a Nand gate

module NAND(in1,in2, out);

input in1, in2;

output out;

// continuous assign statement

assign out = ~(in1 & in2);

endmodule

```

```

In the above example:

<module name>: NAND

<port list>: in1, in2, out

<Declares>: input in1, in2;

output out;

<module items>: assign out = ~(in1 & in2);

```

**Note:** The continuous assignment **assign** continuously watches for changes to variables in its right hand side and whenever that happened the right hand side is re-evaluated and the result immediately propagated to the left hand side (**out**).

- **Structural specification** expresses the behavior of a digital system (module) as a hierarchical interconnection of sub modules.

Here is a structural specification of a module **AND** obtained by connecting the output of one **NAND** to both inputs of another one.

```

module AND(in1, in2, out);

// Structural model of AND gate from two NANDS

input in1, in2;

output out;

wire w1;

// two instantiations of the module NAND

NAND NAND1 (in1, in2, w1);

NAND NAND2 (w1, w1, out);

endmodule

```

This module has two instances of the NAND module called NAND1 and NAND2 connected together by an internal wire w1.

The general form to invoke an instance of a module is:

<module name> <instance name> (<port list>);

## Quartus II Introduction Using Verilog Design:

The following example makes use of the Verilog design entry method, in which the user specifies the desired circuit in the Verilog hardware description language.

#### **1-Getting Started:**

Follow the steps in the previous experiment to create new project, and name it Xor1.

#### **<u>2-Using the Quartus II Text Editor:</u>**

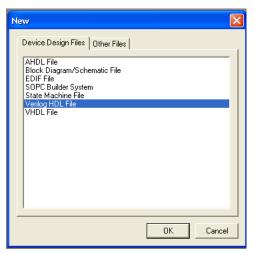

1-Select **File** > **New** to get the window in Figure 1, then choose **Verilog HDL File** and click **OK**. This opens the Text Editor window in Figure 2.

Figure (1)

Figure (2)

2- Specify the name for the file that will be created. Select **File > Save As** to open the pop-up box depicted in Figure 3.

In the box labeled **Save as type choose Verilog HDL File**. In the box labeled **File name type Xor1**. Put a checkmark in the box **Add file to current project**. Click **Save**, which puts the file into the directory Exp2 and leads to the Text Editor window shown in Figure (4).

| Save As                                                            |                             |                                                                                            |           | X              |

|--------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------|-----------|----------------|

| Save in:                                                           | Exp2                        | •                                                                                          | + 🗈 💣 🎟 • |                |

| My Recent<br>Documents<br>Desktop<br>My Documents<br>My Computer   | <mark>с</mark> ањ           |                                                                                            |           |                |

| My Network<br>Places                                               | File name:<br>Save as type: | Xor1       Verilog HDL File (*.v;*.vlg;*.verilog)       Image: Add file to current project | <b>v</b>  | Save<br>Cancel |

|                                                                    |                             | Figure (3)                                                                                 |           |                |

| 😍 Xor1.v                                                           |                             |                                                                                            |           |                |

| □<br>□<br>□<br>□<br>□<br>□<br>□<br>□<br>□<br>□<br>□<br>□<br>□<br>□ |                             |                                                                                            |           |                |

Figure (4)

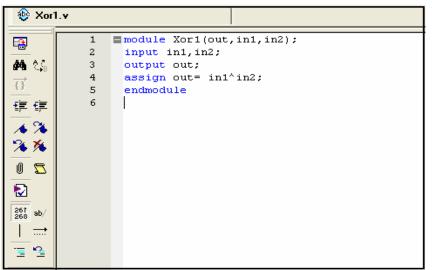

3- Enter the Verilog code as shown in Figure 5. Then save the file by choosing **File > Save**, or by typing the shortcut Ctrl-s.

Figure (5)

### **Using Verilog Templates**